TM 55-4920-401-13&P

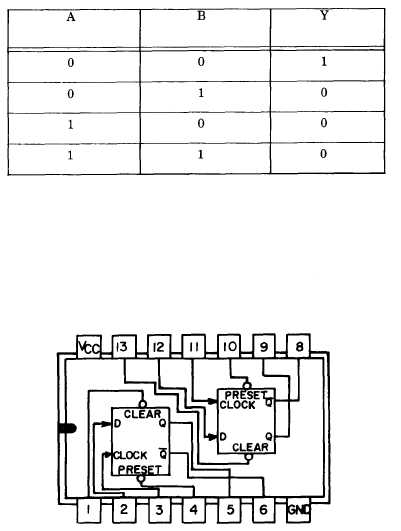

T a b l e 1 - 7 . N O R G a t e T r u t h T a b le

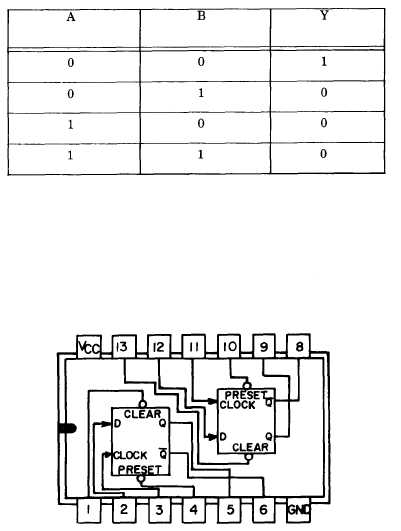

Figure 1-35. Dual D-Type Edge-Triggered Flip-Flop.

9. Dual D-Type Edge-Triggered Flip-

Flop (SN5474). This flip-flop (fig. 1-35) has direct

clear and preset inputs and complementary Q and Q

outputs. Input information is transferred to the out-

puts on the positive edge of the clock pulse. Clock

triggering occurs at a voltage level of the clock

pulse and is not directly related to the transition

time of the positive-going pulse. A low input to clear

sets Q to logic 0. A low input to preset sets Q to logic

1. Clear and preset inputs dominate regardless of

clock and D inputs. Table 1-8 summarizes the input-

output relationships.

10. Dual J-K Master-Slave Flip-Flop

with Preset and Clear (SN5476). The J-K flip-

flop (fig. 1-36) is based on the master-slave prin-

ciple. Inputs to the master section are controlled by

1-36

the clock pulse (fig. 1-37). The clock pulse also regu-

lates the - state of the coupling transistors which

connect the master and slave sections. The sequence

of operation is as follows:

1. Isolate slave from master.

2. Enter information from J and K in-

puts to master.

3. Disable J and K inputs.

4. Transfer information from master

to slave.

Clear and preset are independent of the clock. A low

input to preset sets Q to logic 1. A low input to clear

sets Q to-logic 0. Input-output relationships of each

flip-flop are summarized in table 1-9.